[conference] Accepted at ICNCE 2026

We made an analog RNN that does keyword spotting with less than a microwatt of power -- and it just got accepted at ICNCE 2026!

I’m super happy to share that our paper “Hardware-Algorithm Co-Design of Analog Recurrent Neural Networks for Sub-Microwatt Inference” has been accepted for presentation at ICNCE 2026! ⚡

Always-on AI is everywhere these days – think wake-word detection, activity tracking, or tiny sensor nodes. But there’s a catch: digital chips use milliwatts, which drains batteries fast. Analog circuits are much more efficient, but they suffer from noise and drift. So we asked a different question: what if we could design the neural network itself so that analog noise simply doesn’t matter?

Here’s the trick

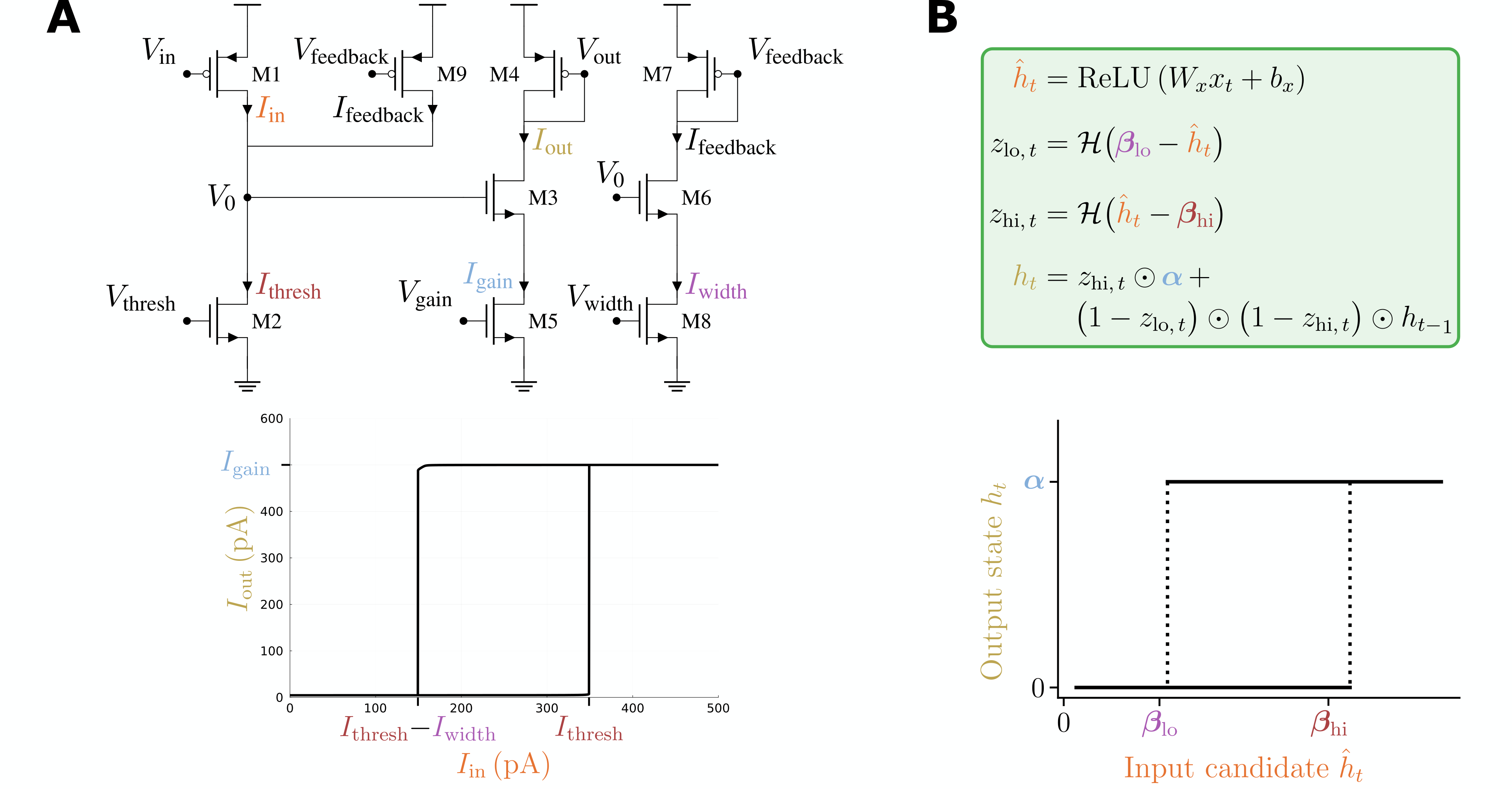

We didn’t try to force a standard RNN into analog hardware. Instead, we used a special kind of recurrent network called a First-Quadrant Bistable Memory Recurrent Unit (FQ BMRU). These units update in discrete steps and hold their state like a little memory – almost exactly what happens naturally in analog current-mode memory cells when they run below threshold. We saw that match and ran with it. Every learned parameter in the network maps directly to a knob on the circuit (like bias currents you can tune on the chip).

The result is a true hardware-algorithm co-design. The network’s discrete nature kills accumulated noise by more than 20x at each cell boundary, so even deep networks stay reliable inside the analog domain.

How a current-mode memory cell maps to the FQ BMRU equations. Every learned parameter becomes a physical circuit element – no more gap between software training and hardware implementation.

How a current-mode memory cell maps to the FQ BMRU equations. Every learned parameter becomes a physical circuit element – no more gap between software training and hardware implementation.

We tested our idea on single-word keyword spotting using the Google Speech Commands dataset. We built a full circuit with 768 transistors in 180 nm CMOS and simulated it in Cadence Spectre. Out of 50 test samples, the analog hardware matched the software predictions in 49 cases – the only mismatch happened on a super close decision. The chip gets >90% accuracy while using only about 100 nW of average power. That’s at least a thousand times less than typical digital implementations.

Working at this intersection of algorithms and circuits was eye-opening. You can get huge efficiency gains when you stop treating hardware and software as separate problems and start designing them together from the start.

Resources

📄 Abstract: ORBI.

🔗 Related preprint: F. De Geeter et al., arXiv:2601.09495, 2026.

🔗 Patent: A. Fyon et al., in press, hdl:2268/338453.

Get in touch: questions or collaborations? Drop me an email at afyon@uliege.be.

Arthur Fyon’s webpage: Arthur Fyon

Loris Mendolia’s webpage: Loris Mendolia

Damien Ernst’s webpage: Damien Ernst

Guillaume Drion’s webpage: Guillaume Drion

Acknowledgments

Can’t wait for ICNCE 2026 – see you there!

This work has been the subject of a patent application under number EP26175243.0. and EP26175248.9.